# RISC-V Instruction Sets Want to be Free!

Andrew Waterman SiFive, Inc. andrew@sifive.com

ASPIRE End of Project Celebration December 5, 2017

# Instruction Set Architectures don't matter

Most of the performance and energy running software on a computer is due to:

- Algorithms

- Application code

- Compiler

- OS/Runtimes

- ISA (Instruction Set Architecture)

- Microarchitecture (core + memory hierarchy)

- Circuit design

- Physical design

- Fabrication process

- In a system, there's also displays, radios, DC/DC converters, sensors, actuators, ...

#### **ISAs do matter**

- Most important interface in computer system

- Large cost to port and tune all ISA-dependent parts of a modern software stack

- Large cost to recompile/port/QA all supposedly ISA-independent parts of stack

- If using proprietary closed-source, don't have code

- Lost your own source code

- Most of the cost of developing a new chip is developing software for it

If choice of ISA doesn't have much impact on system energy/performance, and it costs a lot to use different ones

Why isn't there a free, open standard ISA that everyone can use for everything?

#### **Universal ISA Requirements**

- Works well with existing software stacks, languages

- Is native hardware ISA, not virtual machine/ANDF

- Suits all sizes of processor, from smallest microcontroller to largest supercomputer

- Suits all implementation technologies, FPGA, ASIC, full-custom, future device technologies...

- Efficient for all microarchitecture styles: in-order, decoupled, out-of-order; sequential, superscalar

- Supports extensive specialization to act as base for customized accelerators

- Stable: not changing, not disappearing

- In 2010, after many years and many projects using MIPS, SPARC, and x86 as basis of research, time to look at ISA for next set of projects

- Obvious choices: x86 and ARM

- x86 impossible too complex, IP issues

- ARM mostly impossible no 64-bit, complex, IP issues

just use Alpha?

Andrew N to Krste, Yi

I was thinking of ISA going fo what people do here, and to th an Alpha refere

Krste Asanovic

May 17, 2010 •••

to Andrew, Krste, Yunsup

Trap barriers for correct FP.

No compressed (16-bit) instruction format.

No current or future mind share (MIPS is standard educational ISA, and is still commercially produced).

Oh, and R31 is the zero register.

- In 2010, after many years and many projects using MIPS, SPARC, and x86 as basis of research, time to look at ISA for next set of projects

- Obvious choices: x86 and ARM

- x86 impossible too complex, IP issues

- ARM mostly impossible no 64-bit, complex, IP issues

- So we started "3-month project" in summer 2010 to develop our own clean-slate ISA

- Andrew Waterman, Yunsup Lee, Dave Patterson, Krste Asanovic principal designers

- Four years later, we released frozen base user spec

- But also many tapeouts and several research publications along the way

Why are outsiders complaining about changes

to RISC-V in Berkeley classes?

#### What's Different about RISC-V?

- Simple

- Far smaller than other commercial ISAs

- Clean-slate design

- Clear separation between user and privileged ISA

- Avoids µarchitecture or technology-dependent features

- A modular ISA

- Small standard base ISA

- Multiple standard extensions

- Designed for *extensibility/specialization*

- Variable-length instruction encoding

- Vast opcode space available for instruction-set extensions

- Stable

- Base and standard extensions are frozen

- Additions via optional extensions, not new versions

#### **RISC-V Base Plus Standard Extensions**

- Four base integer ISAs

- RV32E, RV32I, RV64I, RV128I

- RV32E is 16-register subset of RV32I

- Only <50 hardware instructions needed for base

- Standard extensions

- M: Integer multiply/divide

- A: Atomic memory operations (AMOs + LR/SC)

- F: Single-precision floating-point

- D: Double-precision floating-point

- G = IMAFD, "General-purpose" ISA

- Q: Quad-precision floating-point

- All the above are a fairly standard RISC encoding in a fixed 32-bit instruction format

- Above user-level ISA components frozen in 2014

- Supported forever after

RISC-V

#### RV32I / RV64I / RV128I + M, A, F, D, Q, C RISC-V "Green Card"

#### **RISC-V Reference Card**

| Base Integer Instructions (32 64 128) |     |                 |                | RV Privileged Instructions (32 64 128) |                       |        |                                        |            | 3 Optional FP Extensions: RV32{F\D\Q} |                   |            |                      | -                      | nal Compre | T T             | Instrue | ctions: RVC |               |

|---------------------------------------|-----|-----------------|----------------|----------------------------------------|-----------------------|--------|----------------------------------------|------------|---------------------------------------|-------------------|------------|----------------------|------------------------|------------|-----------------|---------|-------------|---------------|

| Category Name                         | Fmt | RV{32 6         | i4 128)I Base  | <b>Category</b>                        | Name                  | Fmt    | RV mnemonic                            |            | Category                              | Name Fr           | mt         | $RV{F D Q} (I$       | HP/SP,DP,QP)           | Category   | Name            | Fmt     |             | RVC           |

| Loads Load Byte                       | Ι   | LB              | rd, rs1, imm   | CSR Access                             | Atomic R/W            | R      | CSRRW rd                               | ,csr,rs1   | Load                                  | Load              | I          | FL{W,D,Q}            | rd, rs1, imm           | Loads      | Load Word       | CL      | C.LW        | rd',rs1',imm  |

| Load Halfword                         | Ι   | LH              | rd, rs1, imm   | Atomic F                               | Read & Set Bit        | R      | CSRRS rd                               | ,csr,rs1   | Store                                 | Store 5           | S I        | FS{W,D,Q}            | rs1, rs2, imm          |            | Load Word SP    | CI      | C.LWSP      | rd, imm       |

| Load Word                             | Ι   | LIWDQ           | rd, rsl, imm   | Atomic Re                              | ad & Clear Bit        | R      |                                        |            | Arithmetic                            | ADD I             | RI         | FADD. {S D Q}        | rd, rs1, rs2           |            | Load Double     | CL      | C.LD        | rd',rsl',imm  |

| Load Byte Unsigned                    |     | LBU             | rd, rs1, imm   |                                        | mic R/W Imm           | R      |                                        | ,csr,imm   |                                       |                   |            | FSUB. {S D Q}        | rd, rs1, rs2           |            | Load Double SP  | CI      | C.IMSP      | rd, imm       |

| Load Half Unsigned                    |     |                 | rd, rs1, imm   | Atornic Read 8                         |                       |        |                                        | ,csr,imm   |                                       |                   |            | EMUL. {S D Q}        | rd, rs1, rs2           | -          | Load Quad       |         |             | rd',rsl',imm  |

| Stores Store Byte                     |     | SB              | rs1, rs2, imm  | Atomic Read &                          |                       |        |                                        | csr, imm   |                                       |                   |            | FDIV.{S D Q}         | rd, rs1, rs2           |            | Load Quad SP    |         |             | rd, imm       |

| Store Halfword                        |     | SH              | rs1, rs2, imm  | Change Level                           |                       |        | ECALL IG                               | , (51, 100 |                                       |                   |            | FSQRT. {S D Q}       | rd, rs1                | Lond       | Byte Unsigned   |         |             | rd',rs1',imm  |

|                                       |     |                 |                | -                                      |                       |        | EBREAK                                 |            | Mul-Add                               |                   |            |                      |                        | -          |                 |         |             |               |

| Store Word                            |     | S{W D Q}        | rs1,rs2,imm    |                                        | nt Breakpoint         |        |                                        |            |                                       |                   |            | $FMADD_{S}   D   Q $ |                        |            | loat Load Word  |         |             | rd',rs1',imm  |

| Shifts Shift Left                     |     |                 | rd, rs1, rs2   |                                        | nment Return          |        | ERET                                   |            |                                       |                   |            |                      | rd,rs1,rs2,rs3         |            | at Load Double  |         |             | rd',rs1',imm  |

| Shift Left Immediate                  |     |                 | rd, rs1, shamt | Trap Redirec                           |                       |        | MRTS                                   |            | -                                     | • •               |            |                      | rd,rs1,rs2,rs3         |            | t Load Word SP  |         |             |               |

| Shift Right                           | R   |                 | rd, rs1, rs2   | Redirect Trap                          |                       |        | MRTH                                   |            |                                       |                   |            |                      | rd,rs1,rs2,rs3         |            | Load Double SP  |         |             |               |

| Shift Right Immediate                 | Ι   | SRLI{ W D}      | rd, rs1, shamt | Hypervisor Trap                        |                       |        | HRTS                                   |            | Sign Inject                           | SiGN source I     | R          | FSGNJ.{S D Q}        | rd, rs1, rs2           | Stores     | Store Word      |         |             | rs1',rs2',imm |

| Shift Right Arithmetic                |     | SRA{   W   D }  | rd, rs1, rs2   | Interrupt Wa                           |                       |        | WFI                                    |            | Negative                              | SiGN source       | R          | FSGNJN.{S D Q}       | rd,rs1,rs2             |            | Store Word SP   |         |             | rs2,imm       |

| Shift Right Arith Imm                 | Ι   | SRAI{ W D}      | rd, rs1, shamt | MMU Sup                                | ervisor FENCE         | R      | SFENCE.VM rs                           | 1          | Xor                                   | r SiGN source     | RI         | FSGNJX.{S D Q}       | rd,rs1,rs2             |            | Store Double    | CS      | C.SD        | rs1',rs2',imm |

| Arithmetic ADD                        | R   | ADD{   W   D}   | rd, rs1, rs2   | Optional                               | Multiply-D            | ivide  | Extension: R                           | V32M       | Min/Max 👘                             | MiNimum I         | R          | FMIN.{S D Q}         | rd, rs1, rs2           | S          | tore Double SP  | CSS     | C.SDSP      | rs2,imm       |

| ADD Immediate                         | Ι   | ADDI [   W   D] | rd, rsl, imm   | Category                               | Name Fmt              |        | RV32M (Mult-D                          | )iv)       |                                       | MAXimum I         | RI         | FMAX.{S D Q}         | rd, rs1, rs2           |            | Store Quad      | CS      | C.SQ        | rs1',rs2',imm |

| SUBtract                              | R   | SUB{ W D}       | rd, rs1, rs2   | Multiply P                             | ULtiply R             | MUL [  | WDJ rd, rs1,                           | , rs2      | Compare Co                            | ompare Float = 1  | RI         | FEQ. [S D Q]         | rd, rs1, rs2           | 1          | Store Quad SP   | CSS     | C.SQSP      | rs2,imm       |

| Load Upper Imm                        | U   | TOI             | rd, imm        | MULtiply up                            |                       | MULH   | rd, rsl,                               |            | -                                     | npare Float < 1   |            |                      | rd, rs1, rs2           |            | oat Store Word  |         |             | rd',rsl',imm  |

| Add Upper Imm to PC                   |     |                 | rd, imm        | MULtiply Half S                        |                       | MULHS  | SU rd, rsl,                            | rs2        |                                       | npare Float ≤ I   |            |                      | rd, rs1, rs2           |            | at Store Double |         |             | rd',rsl',imm  |

| Logical XOR                           |     | XOR             |                | MULtiply upper 1                       |                       | MULHU  |                                        |            |                                       |                   |            | FCLASS [S D Q]       |                        |            | Store Word SP   |         |             |               |

| XOR Immediate                         |     | XORI            |                | Divide                                 |                       | DIA1   |                                        |            |                                       | e from Integer    |            |                      | rd, rs1                | -          | tore Double SP  |         |             |               |

| OR                                    | ~   |                 |                | DIVICE<br>DIVide U                     |                       | DIAN   |                                        |            |                                       |                   |            |                      | rd, rs1                | Arithmeti  |                 |         |             |               |

|                                       |     | OR              | rd, rs1, rs2   |                                        |                       |        | rd, rs1,                               |            |                                       | ove to Integer I  |            |                      |                        | Anumeu     |                 |         | C.ADD       | rd, rsl       |

| OR Immediate                          | ~   | ORI             | rd, rs1, imm   | RemainderRE                            |                       |        | ₩ D} rd,rs1,                           |            |                                       |                   |            | FCVT.{S D Q}.W       |                        |            | ADD Word        |         |             | rd',rs2'      |

| AND                                   |     | AND             | rd, rs1, rs2   | REMainder U                            |                       |        | [ W D] rd,rs1,                         |            |                                       | Arre Orres arrest |            | FCVT.{S D Q}.W       |                        |            | DD Immediate    |         |             | rd, imm       |

| AND Immediate                         |     | ANDI            | rd, rs1, imm   | -                                      |                       |        | ion Extension                          |            |                                       |                   |            | FCVT.W.{S D Q}       |                        |            | ADD Word Imm    |         |             | rd, imm       |

| Compare Set <                         | R   | SLT             | rd,rs1,rs2     | Category                               | Name Fmt              |        | {32 64 128}A (/                        |            |                                       |                   |            | FCVT.WU.{S D Q       | <pre>p} rd,rs1</pre>   | -          | D SP Imm * 16   |         |             |               |

| Set < Immediate                       | Ι   | SLTI            | rd, rs1, imm   | Load Load R                            | eserved R             | LR. {) | <pre>IDQ} rd,</pre>                    | , rsl      | Configurati                           | on Read Stat      | R          | FRCSR                | rd                     | AI         | DD SP Imm * 4   | CIW     | C.ADDI4:    | SPN rd',imm   |

| Set < Unsigned                        | R   | SLTU            | rd, rs1, rs2   | Store Store Co                         | nditional R           | SC. [1 | <pre>v D Q} rd,</pre>                  | ,rs1,rs2   | Read Ro                               | unding Mode       | RI         | FRRM                 | rd                     | L          | oad Immediate   | CI      | C.LI        | rd, imm       |

| Set < Imm Unsigned                    | Ι   | SLTIU           | rd, rs1, imm   | Swap                                   | SWAP R                | AMOST  | NAP.{W D Q} rd,                        | ,rs1,rs2   |                                       | Read Flags        | RI         | FRFLAGS              | rd                     | Lo         | oad Upper Imm   | CI      | C.LUI       | rd, imm       |

| Branches Branch =                     | SB  | BEQ             | rs1,rs2,imm    | Add                                    | ADD R                 | AMOAI  | $DD_{\mathbb{T}} \{ W   D   Q \} $ rd, | rs1, rs2   | Swa                                   | p Status Reg   I  | RI         | FSCSR                | rd, rsl                |            | MoVe            | CR      | C.MV        | rd, rsl       |

| Branch ≠                              | SB  | BNE             | rs1, rs2, imm  | Logical                                | XOR R                 | AMOXO  | DR.{W D Q} rd,                         | rs1, rs2   | Swap Ro                               | unding Mode       | RI         | FSRM                 | rd, rsl                |            | SUB             | CR      | C.SUB       | rd',rs2'      |

| Branch <                              | SB  | BLT             | rs1,rs2,imm    | _                                      | AND R                 | AMOAN  | WD. [W D Q] rd,                        | rs1, rs2   | -                                     | Swap Flags        | RI         | FSFLAGS              | rd, rsl                |            | SUB Word        | CR      | C.SUBW      | rd',rs2'      |

|                                       |     | BGE             | rs1,rs2,imm    |                                        |                       |        |                                        |            | Swan Roundin                          | •                 |            | FSRMI                | rd, imm                | Logical    | XOR             |         | C.XOR       | rd', rs2'     |

| Branch < Unsigned                     |     | BLTU            | rs1, rs2, imm  | Min/Max M                              | Nimurn R              |        | $[N_{W}]D[Q] rd,$                      |            | •                                     | ap Flags Imm      |            |                      | rd, imm                |            |                 | cs      |             | rd', rs2'     |

| Branch ≥ Unsigned                     |     |                 | rs1, rs2, imm  |                                        | Ximum R               |        | $X_{W D Q}$ rd,                        |            |                                       |                   |            | ns: RV{64 12         |                        |            |                 |         | C.AND       | rd', rs2'     |

|                                       |     |                 |                |                                        |                       |        |                                        |            | Category                              | Name Fr           |            |                      |                        | · .        | AND Immediate   |         |             |               |

|                                       |     | JAL             | rd, imm        | MINimum U                              |                       |        | [NU.{W D Q} rd,                        | ,101,100   |                                       | e from Integer    | _          |                      | rd, rsl                |            |                 |         |             | rd', rs2'     |

| Jump & Link Register                  |     | JALR            | rd, rs1, imm   | MAXimum U                              | nsigned R             | AMON?  | $XU.{W D Q}$ rd,                       | , rs1, rs2 |                                       |                   |            |                      |                        |            | Shift Left Imm  |         |             | rd, imm       |

| Synch Synch thread                    | I   | FENCE           |                |                                        |                       |        |                                        |            |                                       | ove to Integer I  |            |                      | rd, rsl                | -          | ight Immediate  |         |             | rd',imm       |

| Synch Instr & Data                    | 1   | FENCE.I         |                |                                        |                       |        |                                        |            |                                       |                   |            | FCVT.{S D Q}.{       |                        |            | Sight Arith Imm | ++      |             | rd',imm       |

| System System CALL                    |     | SCALL           |                |                                        | Ing IT.               |        |                                        |            |                                       |                   |            | FCVT.{S D Q}.{       |                        | Branches   |                 |         |             | rsl',imm      |

| System BREAK                          | Ι   | SBREAK          |                | 16-bit (RVC)                           | and 32-bit i          | lnstri | uction Formats                         |            |                                       |                   |            | FCVT.{L T}.{S        |                        |            | Branch≠0        | CB      | C.BNEZ      | rs1',imm      |

| Counters ReaD CYCLE                   | Ι   | RDCYCLE         | rd             | 15 14 29 1                             | 9 11 10 0 9           | 7 6    | 5 4 9 9 1 0                            |            | Convert to                            | Int Unsigned      | R I        | FCVT.{L T}U.{S       | D Q} rd,rs1            | Jump       | Jump            | CJ      | C.J         | imm           |

| ReaD CYCLE upper Half                 | Ι   | RDCYCLEH        | rd             | CI 15 14 13 1<br>funct4                | 2 11 10 9 8<br>rd/rs1 | 1 0    | 5 4 3 2 1 0<br>rs2 op                  |            |                                       |                   |            |                      |                        |            | Jump Register   | CR      | C.JR        | rd, rsl       |

| ReaD TIME                             | Ι   | RDTIME          | rd             | CSS funct3 in                          |                       |        | imm op R                               | 31         | 30 25 24                              |                   | ur1        |                      | 8 7 6 0                | Jump & Li  | ink J&L         | CJ      | C.JAL       | imm           |

| ReaD TIME upper Half                  | Ι   | RDTIMEH         | rd             | CIW funct3                             | imm                   |        | rs2 op I                               | 1          | inct7<br>imm[11:0]                    |                   | rs1<br>rs1 |                      | rd opcode<br>rd opcode | Jump       | & Link Register | CR      | C.JALR      | rs1           |

| ReaD INSTR RETired                    | Ι   | RDINSTRET       |                | CL funct3                              | imm                   |        | rd' op 💊                               | im         | m[11:5]                               |                   | rsi        |                      | m 4:0 opcode           | System     | Env. BREAK      |         |             |               |

| ReaD INSTR upper Half                 |     |                 |                | CS funct3                              | imm rsl'<br>imm rsl'  | imn    |                                        |            | imm[10:5]                             |                   | rsl        |                      | imm[11] opcode         |            |                 |         |             |               |

|                                       |     | Control METH    |                | CB funct3                              | offset rs1'           | unn    | n rs2' op 5<br>offset op U             |            |                                       | imm[31:12]        |            |                      | rd opcode              |            |                 |         |             | 12            |

|                                       |     |                 |                | CI funct3                              | jump t                | arget  | onset op U                             |            | imm[10:1]                             |                   | im         |                      | rd opcode              |            |                 |         |             | 12            |

|                                       |     |                 |                | U                                      |                       | ~      | 0                                      |            |                                       |                   |            |                      |                        |            |                 |         |             |               |

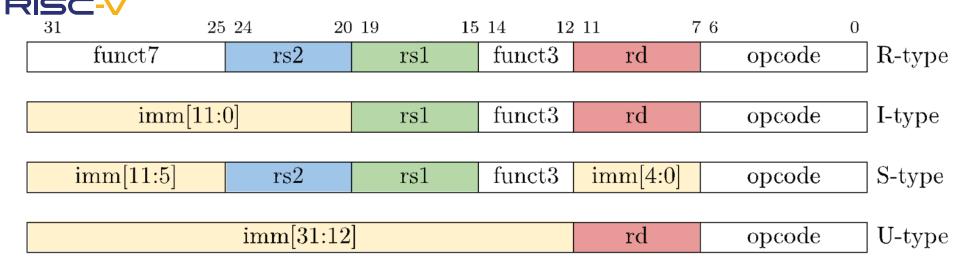

#### **RISC-V Standard Base ISA Details**

- 32-bit fixed-width, naturally aligned instructions

- 31 integer registers x1-x31, plus x0 zero register

- rd/rs1/rs2 in fixed location, no implicit registers

- Immediate field (instr[31]) always sign-extended

- Floating-point adds f0-f31 registers plus FP CSR, also fused mul-add four-register format

- Designed to support PIC and dynamic linking

#### **Variable-Length Encoding**

| RISC-V        |               |                    | xxxxxxxxxxxxaa   | 16-bit (aa $\neq$ 11)              |

|---------------|---------------|--------------------|------------------|------------------------------------|

|               |               | r                  |                  |                                    |

|               |               | *****              | xxxxxxxxxbbb11   | $32$ -bit (bbb $\neq$ 111)         |

|               |               |                    | 24444            | 40.1.4                             |

|               | ···xxxx       | ******             | xxxxxxxx011111   | 48-bit                             |

|               |               |                    | 0111111          | 61 bit                             |

|               | ···XXXX       | XXXXXXXXXXXXXXXXXX | xxxxxxxx0111111  | 64-bit                             |

|               | ···xxxx       | *****              | xnnnxxxxx1111111 | $(80+16*nnn)$ -bit, nnn $\neq$ 111 |

|               |               |                    |                  |                                    |

|               | $\cdots xxxx$ | *****              | x111xxxxx1111111 | Reserved for $\geq 192$ -bits      |

| Byte Address: | base+4        | base+2             | base             |                                    |

- Extensions can use any multiple of 16 bits as instruction length

- Branches/Jumps target 16-bit boundaries even in fixed 32-bit base

- Consumes 1 extra bit of jump/branch address

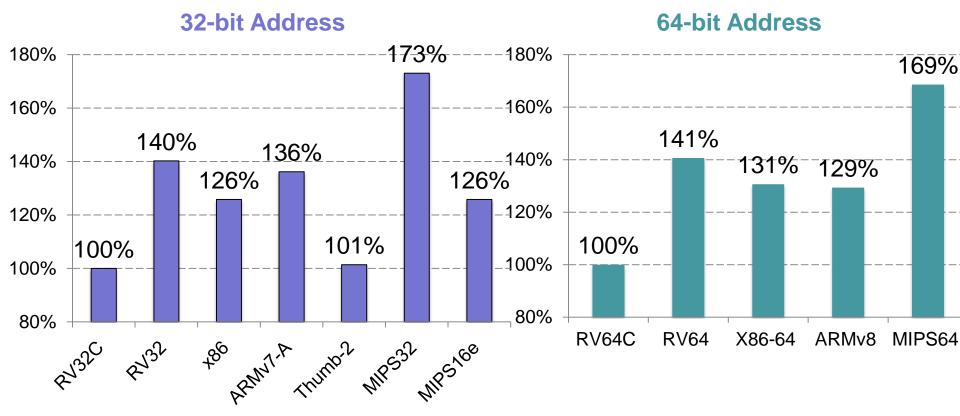

### **"C": Compressed Instruction Extension**

- Compressed code important for:

- low-end embedded to save static code space

- high-end commercial workloads to reduce cache footprint

- C extension adds 16-bit compressed instructions

- 2-operand instructions only

- Most instructions can only access 8 registers

- 1 compressed instruction expands to 1 base instruction

- Assembly lang. programmer & compiler oblivious

- All original 32-bit instructions retain encoding but now can be 16-bit aligned

- 50%-60% instructions compress ⇒ 25%-30% smaller

#### SPECint2006 compressed code size with save/restore optimization (relative to "standard" RVC)

RISC-V now smallest ISA for 32- and 64-bit addresses

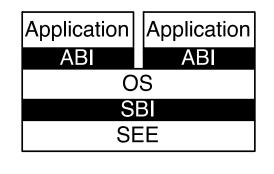

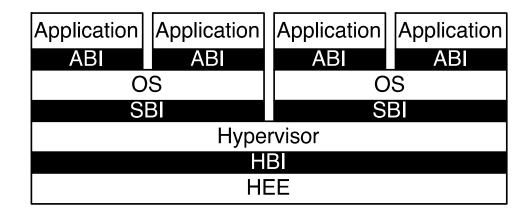

#### **RISC-V Privileged Architecture**

Application ABI AEE

Modular design supports many classes of system

- Simple embedded systems with no protection

- Embedded systems with protection

- Unix-class systems with page-based virtual memory

- Hypervised Unix systems with two-level paging

#### **RISC-V Foundation**

- Mission statement

- "to standardize, protect, and promote the free and open RISC-V instruction set architecture and its hardware and software ecosystem for use in all computing devices."

- Established as a 501(c)(6) non-profit corporation on August 3, 2015

- Now >100 members

- 10s of companies participating in standards definition

#### Summary: Why RISC-V?

- Free and open architecture, no proprietary lock-in

- Much simpler ISA than others

- Readily and freely extensible

- Usable as base ISA for every core on SoC

- RISC-V project goal: become the industry-standard ISA for all computing devices

- Thank you for sponsoring this research!

## **Questions**?