# Chisel 2.0.0 to Chisel 3.0.0

Because everybody loves a trilogy

Presentation by Adam Izraelevitz

A long time ago, in a laboratory (not) far, far away....

### **Generators: Type-Safe Meta-Programming for RTL**

**Design Reuse**

Type-Safety

**Powerful Language Features**

#### **Hired Jonathan Bachrach**

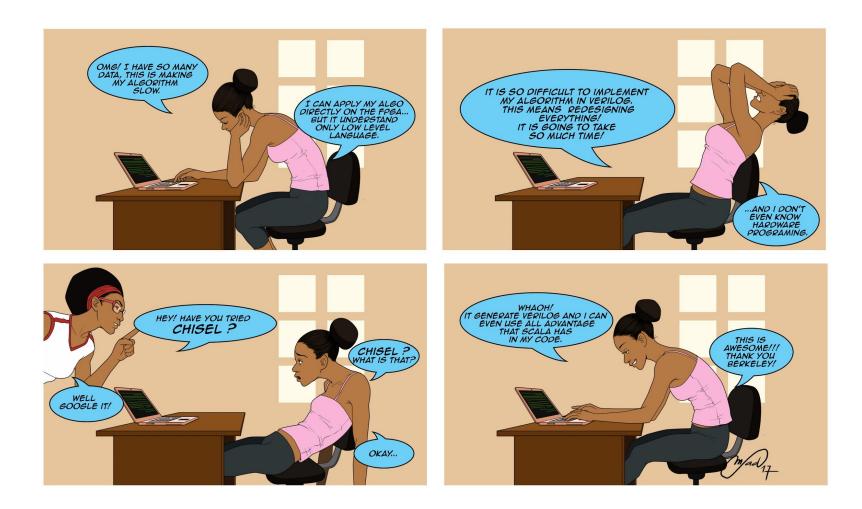

#### Chisel: Constructing Hardware in a Scala Embedded Language

Jonathan Bachrach, Huy Vo, Brian Richards, Yunsup Lee, Andrew Waterman, Rimas Avižienis, John Wawrzynek, Krste Asanović EECS Department, UC Berkeley -{jrb|buytbvo|richards/yunup|vaterman|rims|johnv|krste}beces.berkeley.edu

#### ABSTRACT

In this paper we introduce Chied, a new hardware constrution hanguage that supports advanced individue design using highly parameterized generators and layered domain-specific hardware languages. By embedding Chies in the Scala programming language, we raise the level of hardware design abstration by providing concepts including object orientation, functional programming, parameterized types, and type inscentration support to the strategiest of the strategiest encounts oxforware simulator, or low-seed Veriol edisgined to map to either FPGAs or to a standard ASIC flow for symthesis. This paper presents Chies, its embedding in Scala, hardware examples, and results for C++ simulation, Veriog emulation and ASIC synthesis.

#### Categories and Subject Descriptors

B.6.3 [Logic Design]: [Design Aids – automatic synthesis, hardware description languages]

#### **General Terms**

Design, Languages, Performance

#### Keywords

CAD

#### 1. INTRODUCTION

The dominant traditional hardware-description languages (HDLs), Verilog and VHDL, were originally developed as hardware simulation languages, and were only later adopted as a basis for hardware synthesis. Because the semantics of these languages are based around simulation, synthesizable

Research supported by DoE Award DE-SC0003624, and by Microsoft (Award #024263) and Intel (Award #024894) funding and by matching funding by U.C. Discovery (Award #DIG07-10227).

Permission to make digital or hard copies of all or part of this work for personal or classroom use is grande without fce provided that copies are not make or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy advantise, to republish, to past on server or to redistribute to lists, requires prior specific permission and/or a fee. DAC 2012, June 3-7, 2012, San Francisco, California, USA. Convertien 2012 AM 973-14901-1199-11/2016. S10.00. designs must be inferred from a subset of the language, complicating tool development and designer charaction. These languages also lack the powerful abstraction facilities that are common in modern software languages, which leads to low designer productivity by making it difficult to reuse components. Construing efficient hardware designs requires extensive design-space exploration of alternative system micovarient curreng b) but these traditional HDLs have limited module generation facilities and are lifesuited to producing and composing the highly parameterized module generators near extension angionet the highly parameterized module generators mean angionet these limitations one common anoreach

is to use another language as a macro processing language for an underlying HDL. For example, Genesis2 uses Perl to provide more flexible parameterization and elaboration of hardware blocks written in SystemVerilog [9]. The language called Verischemelog [6] provides a Scheme syntax for specifying modules in a similar format to Verilog. JHDL [1] equates Java classes with modules. HML [7] uses standard ML functions to wire together a circuit. These approaches allow familiar and powerful languages to be macro languages for hardware netlists, but effectively require leaf components of the design to be described in the underlying HDL. This combined approach is cumbersome, combining the poor abstraction facilities of the underlying HDL with a completely different high-level programming model that does not understand hardware types and semantics. An alternative approach is to begin from a domain-specific

application programming language from which a hardware block is generated. Esterel [2] uses event-based statements to program hardware for reactive systems. DIL [4] is an intermediate language targeted at stream processing and hardware virtualization. Bluespec [3] supports a general concurrent computation model, based on guarded atomic actions. While these can provide great designer productivity when the task in hand matches the pattern encoded in the application programming model, they are a poor match for tasks outside their domain. For example, the design of a programmable microprocessor is not well described in a stream programming model, and guarded atomic actions are not a natural way to express a high-level DSP algorithm. Furthermore, in general it is difficult to derive an efficient microarchitecture from a higher-level computation model, especially if the goal is a programmable engine to run many applications, where the human designer would prefer to write a

#### At the end of ParLab, we solved hardware design

## ParLab Chip Highlight Reel

# And so, the problem of hardware design was forever solved.

# Just kidding.

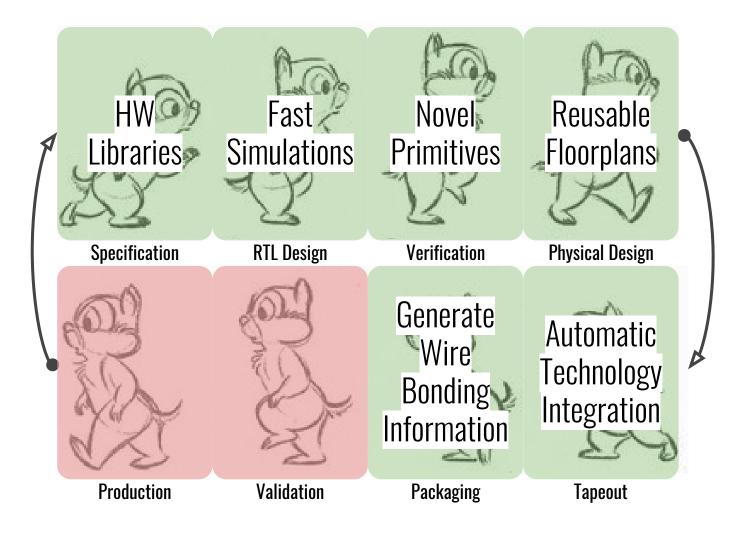

## Solving Hardware Design ≠ Solving The Hardware Design Loop

\* from "How to Draw Chip and Dale booklet". (Walt Disney, 1955)

### What had to change?

CODE URITTEN IN HASKELL IS GUARANTEED TO HAVE

NO SIDE EFFECTS.

Hardware Design Ecosystem Stable and User-Friendly API

**External Collaborations**

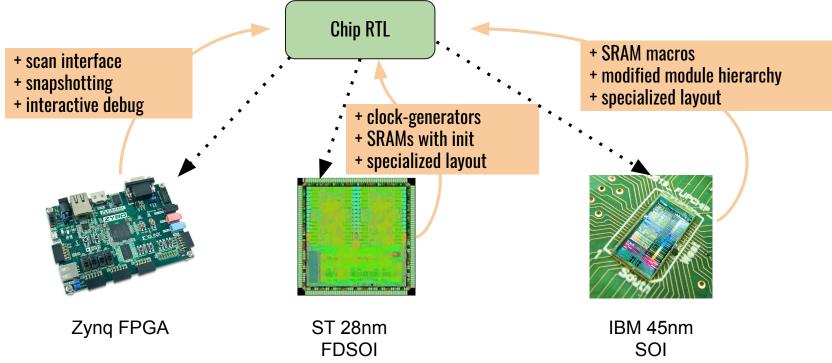

### Platform-Specific or Application-Specific RTL Changes

### What were we doing?

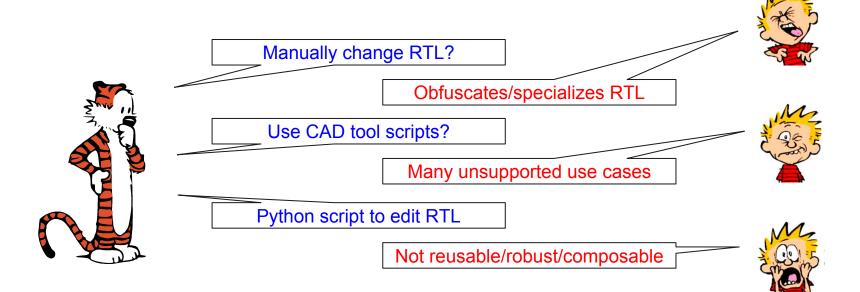

\* from http://www.zoom-comics.com/wp-content/uploads/sites/36/2011/01/calvin-and-hobbes-faces.jpg, accessed 10/23/17

\* from https://useravatar.services.amuniversal.com/user\_avatars/avatars\_gocomicsver3/3001000/3001618/IMG\_7625.GIF, accessed 10/23/17 15

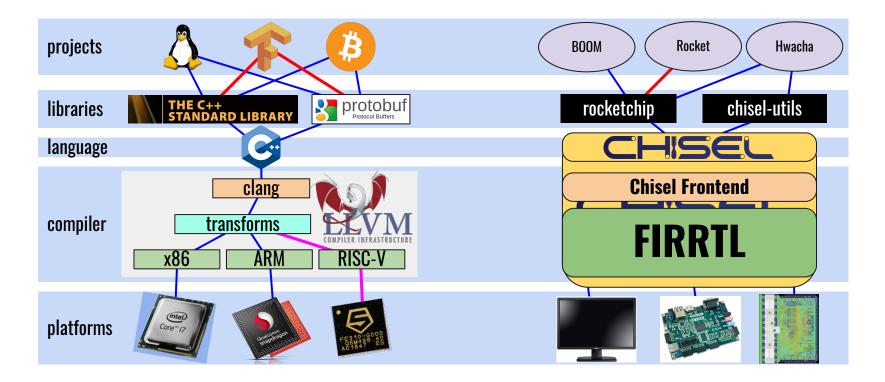

### Realization: We need a software stack, but for hardware

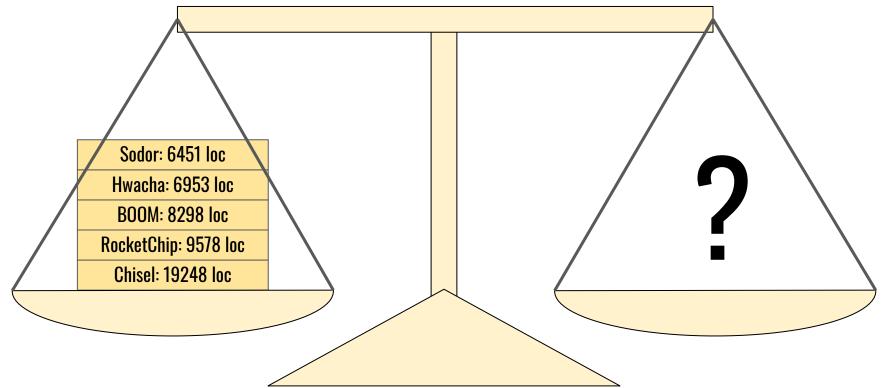

### Second-System-Syndrome: But... do we *really* need all that?

### For impact, we need an ecosystem

## Developing, Porting, Code Reviews, Testing, and so forth

Spring 2015 Summer 2015 Fall 2015 Winter 2015 Spring 2016 Summer 2016 Fall 2016 Winter 2016 Spring 2017 **Summer 2017** Fall 2017

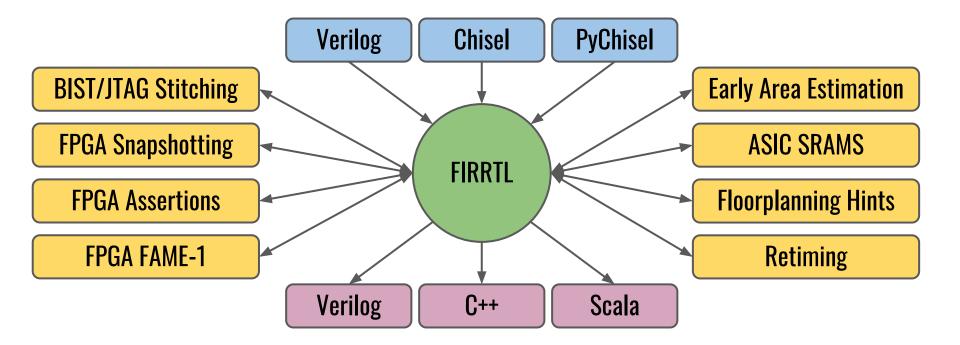

**Designed FIRRTL Compiler Designed Chisel 3 Frontend** Ported RocketChip **Ported Chisel Testers** Added Fixed-Point Type Added Analog Type Added withClock **Released Chisel 3.0.0**

Released FIRRTL 1.0.0

# Chisel 3.0.0 and FIRRTL 1.0.0 have been released!

#### • Projects

- FireSim Datacenter Emulation on FPGAs

- Strober Fast+Accurate Power Sims. for Long Programs

- Hurricane 2 Multi-Core DVFS (Sub-Core)

#### • Transformations

- Quick (and Semi-Accurate) Timing and Area Estimation

- Automatic Combinational Cycle Removal

- $\circ$  Snapshotting and Hardware Assertions for FPGAs

#### • New Features

- Hardware Types vs Hardware Components

- New types (e.g. Complex, DspReal, Fixed-Point, Analog)

- Chisel Library support (annotations)

- $\circ \quad \ \ \, \text{Invalidate API for safer connections}$

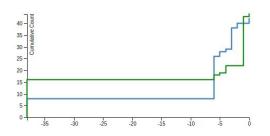

#### Intel: Fast and Semi-Accurate FIRRTL Timer

#### Chisel Source

| 134                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------|

| 135 va.io.in1 	TypeRepacker(DecoupledStage(accin1.io.acc out), to = va.io.in1.bits)                                      |

| 136 va.io.in2                                                                                                            |

| 137                                                                                                                      |

| 138 accout.io.acc data in <> TypeRepacker(DelayModel(DecoupledStage(va.io.out), 10, 2), to = accout.io.acc data in.bits) |

| 139 //accout.io.acc data in <> TypeRepacker(DecoupledStage(va.io.gout), to = accout.io.acc data in.bits)                 |

| 140                                                                                                                      |

| 140 accin1.io.acc in ⇔ io.acc rd reg1                                                                                    |

| 141 accini to accini o to accini equ                                                                                     |

|                                                                                                                          |

|                                                                                                                          |

| 144                                                                                                                      |

| 145 }                                                                                                                    |

| 146                                                                                                                      |

| 147 - class VecAddMulDP[T <: UInt](gen : T, vecLen : Int)(implicit params : AccParams) extends SDFActor(2,1) {           |

| 148 - override lazy val io = IO(new ActorIO {                                                                            |

| <pre>149 val in1 = In(Vec(vecLen, gen), 1)</pre>                                                                         |

| 150 val in2 = In(Vec(vecLen, gen), 1)                                                                                    |

| 151 val out = Out(Vec(vecLen, gen), 1)                                                                                   |

| 152 })                                                                                                                   |

| 153                                                                                                                      |

| 154 - override def func = {                                                                                              |

| <pre>155 val add = Vec.tabulate(vecLen) {i =&gt; io.in1.bits(i) + io.in2.bits(i) }</pre>                                 |

| <pre>156 val mul1 = Vec.tabulate(vecLen) {i =&gt; io.in1.bits(i) * add(i) }</pre>                                        |

| 157 val mul2 = Vec.tabulate(veclen) {i => io,in2,bits(i) } add(i)                                                        |

| 158 val add2 = Vec.tabulate(veclen) {i => mul1(i) + mul2(i) }                                                            |

| 159 val aula - vec.tablate(veclen) $\{i \Rightarrow motif(j) + motif(j)\}$                                               |

| 159 val mula = vec.tabulate(vecten) $\{i = mul2(i) * add2(i)\}$                                                          |

| 160 val $m(t_1 - vec.tabulate(veclen) \{t_1 - m(t_2(t_1) - m(t_2(t_1)))\}$                                               |

| 101 var adus = vect aduste (vecter) (t => Muts(t) + Muts(t) ]<br>162 io.out.bits := add3                                 |

|                                                                                                                          |

| 163 }                                                                                                                    |

| 164 }                                                                                                                    |

| 165                                                                                                                      |

| 166 - class VecAddMulDPWStages[T <: UInt](gen : T, vecLen : Int)(implicit params : AccParams) extends Module {           |

| 167                                                                                                                      |

| 168 - val io = IO(new ActorIO {                                                                                          |

| <pre>169 val in0 = In(UInt((gen.getWidth*vecLen).W), 1)</pre>                                                            |

|                                                                                                                          |

|                                                                                                                          |

#### Start Points

#### Slack Source

| - 38 | DecoupledStage\$out_bits_0#ps            |

|------|------------------------------------------|

| - 38 | <pre>DecoupledStage\$out_bits_1#ps</pre> |

| - 38 | <pre>DecoupledStage\$out_bits_2#ps</pre> |

| - 38 | DecoupledStage\$out_bits_3#ps            |

| - 38 | DecoupledStage\$out_bits_4#ps            |

| - 38 | DecoupledStage\$out_bits_5#ps            |

|      |                                          |

#### **End Points**

#### Slack Sink

| - 38 | DecoupledPipe\$DecoupledStage\$out_bits_0#ns            |

|------|---------------------------------------------------------|

| - 38 | <pre>DecoupledPipe\$DecoupledStage\$out_bits_1#ns</pre> |

| - 38 | DecoupledPipe\$DecoupledStage\$out_bits_2#ns            |

| - 38 | DecoupledPipe\$DecoupledStage\$out_bits_3#ns            |

| - 38 | DecoupledPipe\$DecoupledStage\$out_bits_4#ns            |

| - 38 | DecoupledPipe\$DecoupledStage\$out_bits_5#ns            |

|      |                                                         |

| Ор             | Incr | Required | Net                           |

|----------------|------|----------|-------------------------------|

| connect        | 0    | 38       | DecoupledStage\$out_bits_0#ps |

| connect        | 0    | 38       | DecoupledStage\$io_out_bits_0 |

| add,((16,16))  | 5    | 38       | va\$io_in1_bits_0             |

| tail,((17))    | 0    | 33       | va\$_T_254                    |

| connect        | 0    | 33       | va\$_T_255                    |

| mul,((16,16))  | 8    | 33       | va\$_T_272_0                  |

| connect        | 0    | 25       | va\$_T_304                    |

| add,((32,32))  | 6    | 25       | va\$_T_314_0                  |

| tail,((33))    | 0    | 19       | va\$_T_325                    |

| connect        | Θ    | 19       | va\$_T_326                    |

| mul,((32,32))  | 10   | 19       | va\$_T_343_0                  |

| connect        | 0    | 9        | va\$_T_354                    |

| add,((64,64))  | 7    | 9        | va\$_T_364_0                  |

| tail,((65))    | 0    | 2        | va\$_T_396                    |

| connect        | Θ    | 2        | va\$_T_397                    |

| mux,((1),(64)) | 1    | 2        | va\$_T_414_0                  |

|                | ^    | ,        |                               |

### What had to change?

A Chisel Compiler

Stable and User-Friendly API

**External Collaborations**

### **Emphasis on Clarity**

| Chisel 2.0.0 | Reg(UInt(3))           | 1.<br>2.<br>3.<br>4. | Register of type UInt, width of 3<br>Register whose next cycle's value is 3<br>Register whose initial value is 3<br>Register no initial value and width of 2 |

|--------------|------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chisel 3.0.0 | Reg(UInt(3.W))         | 1.                   | Register of type UInt, width of 3                                                                                                                            |

|              | RegNext(3.U)           | 2.                   | Register whose next cycle's value is 3                                                                                                                       |

|              | RegInit(3.U)           | 3.                   | Register whose initial value is 3                                                                                                                            |

|              | Reg(chiselTypeOf(3.U)) | 4.                   | Register no initial value and width of 2                                                                                                                     |

### Less Error-Prone API's

```

Chisel

def func[T<:Chisel.Data](other: T) = {</pre>

2.0.0

io.out := Reg(null.asInstanceOf[T], next = other, null.asInstanceOf[T])

[info] [0.000] Elaborating design...

[info] [0.022] Done elaborating.

Chisel

def func[T<:Chisel.Data](other: T) = {</pre>

3.0.0

io.out := RegNext(other)

[info] [0.000] Elaborating design...

[info] [0.022] Done elaborating.

```

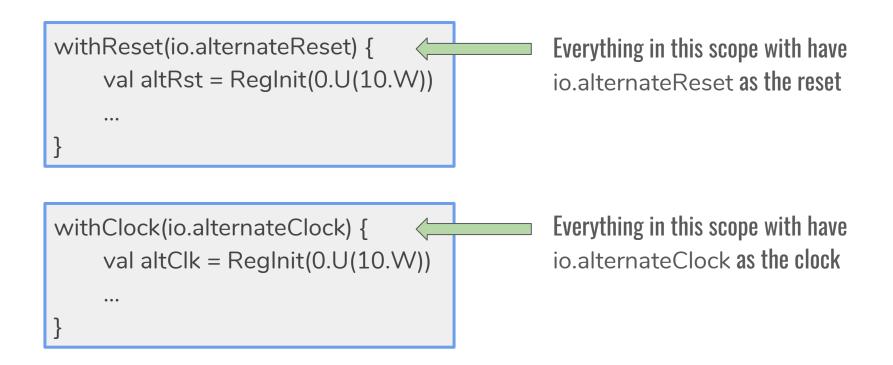

### Lightweight Support for Multi-Clock/Reset

## **Exciting Future Work: The Unified Chisel Tester**

• Fragmented Landscape

- BasicTester (Hardware Testing Hardware)

- PeekPokeTester (Interactive and Slow)

- AdvancedTester (Limited Concurrency)

- Unified Chisel Tester

- Lightweight, powerful, fast

- Multiple circuit drivers, multithreaded

- Integration with Verilator, VCS, Interpreter

- If you have thoughts send them our way!

### What had to change?

A Chisel Compiler

Stable and User-Friendly API

**External Collaborations**

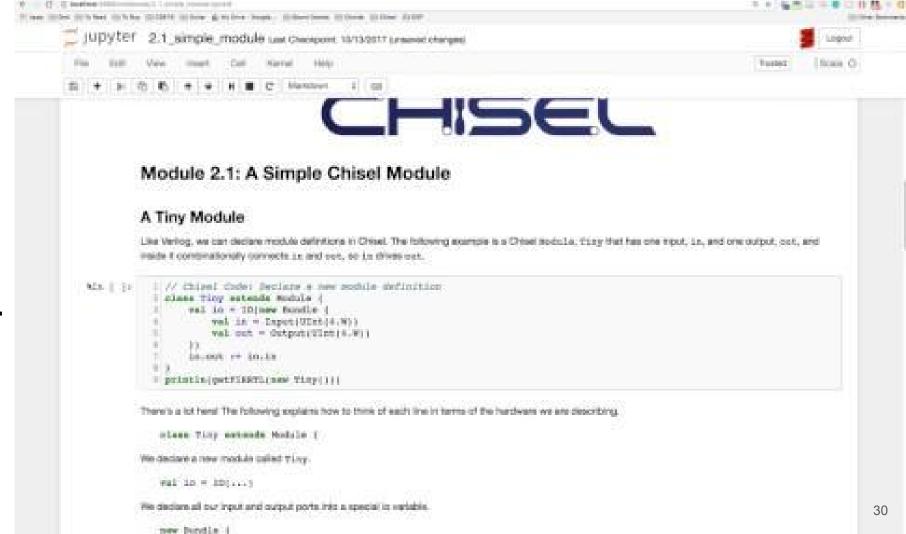

### **Documentation, Documentation, Documentation**

#### Home

Jim Lawson edited this page 23 days ago · 30 revisions

#### Welcome to the Chisel 3 wiki!

If you are completely new to Chisel, check out A Short Users Guide to Chisel.

Chisel is constantly being improved. See the latest Release Notes.

For migrating from Chisel 2 to Chisel 3, check out Chisel3 vs Chisel2.

The ScalaDoc for Chisel3 is available at the API tab on the Chisel web site.

For useful design patterns, see the Cookbook.

For cool new features on the leading and bleeding edge, see Experimental Features.

If you're developing a Chisel library, see Developers.

#### Other interesting pages:

Frequently Asked Questions

nan an taran an

Edit New Page

1

Cookbook

Pages 67

Home

- Frequently Asked Questions

- Troubleshooting

- · Printing in Chisel

- A Short Users Guide to Chisel

- i. Introduction

- ii. Hardware Expressible in Chisel

- iii. Datatypes in Chisel

- iv. Combinational Circuits

- v. Builtin Operators

- vi. Functional Abstraction

- vii. Bundles and Vecs

### **Open-Development via Github Issues/Pull Requests**

| ₽ freech                                                                         | ipsproject / chisel3                                                                                                                                                   | O Unwatch ▼  | 62 🛧 Star | 243 ¥ F    | ork 76 |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|------------|--------|--|--|--|--|--|--|--|

| <> Code ① Issues 78 ① Pull requests 12 Projects 0 	 E Wiki 	 Insights 	 Settings |                                                                                                                                                                        |              |           |            |        |  |  |  |  |  |  |  |

| Filters -     Q is:pr is:open     Labels     Milestones                          |                                                                                                                                                                        |              |           |            |        |  |  |  |  |  |  |  |

| 🗆 IJ.                                                                            | 12 Open ✓ 369 Closed Author - Labels - Projects -                                                                                                                      | Milestones - | Reviews - | Assignee - | Sort - |  |  |  |  |  |  |  |

| ສ                                                                                | Fixed X-pessimism in RRArbiter •<br>#724 opened 7 days ago by pentin-as • Review required                                                                              |              |           |            |        |  |  |  |  |  |  |  |

| ສ                                                                                | Auto clone type □ ✓<br>#723 opened 11 days ago by ducky64 • Review required                                                                                            |              |           |            |        |  |  |  |  |  |  |  |

| <b>n</b>                                                                         | [wip] BoringUtils / Synthesizable Cross Module References • API Addition DO NOT MERGE<br>#718 opened 25 days ago by seldridge • Review required Review required 0 of 3 |              |           |            |        |  |  |  |  |  |  |  |

| 🗆 ม                                                                              | Add issue and pull_request templates. ✓         #713 opened on Nov 3 by ucbjrl • Approved         ₽ 3 of 8                                                             |              |           |            |        |  |  |  |  |  |  |  |

| 🗆 🕻                                                                              | Aggregates can now be marked as literals. ×<br>#694 opened on Sep 15 by grebe • Changes requested                                                                      |              |           |            |        |  |  |  |  |  |  |  |

### **Stack Overflow!**

| 🖹 stack          | overfl                                                                                                                                                                                               | ow      | Questions    | Developer Jobs                          | Tags        | Users       | [chisel] |                         |                |                     | ? 0     | ₽ | Log In | Sign Up      |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|-----------------------------------------|-------------|-------------|----------|-------------------------|----------------|---------------------|---------|---|--------|--------------|--|

| Tagged Questions |                                                                                                                                                                                                      |         |              | info                                    | newest      | frequent    | votes    | active                  | unanswered     | 200<br>questions    | tagged  |   |        | Ask Question |  |

|                  |                                                                                                                                                                                                      |         |              | ction language develors and layered dom |             |             |          | s advanced              | hardware       |                     | about » |   |        |              |  |

| learn more       | top use                                                                                                                                                                                              | ers syn | ionyms       |                                         |             |             |          |                         |                | Related             | Tags    |   |        |              |  |

|                  |                                                                                                                                                                                                      |         |              |                                         |             |             |          |                         |                | scala ×             | 78      |   |        |              |  |

| 1                | Floatin                                                                                                                                                                                              | ng Poir | nt Unit - Op | en Source Hardw                         | ware Imp    | lementati   | on       |                         |                | riscv × :           | 37      |   |        |              |  |

| vote             |                                                                                                                                                                                                      |         |              | Overflow really make                    |             |             |          | k a question            | here - having  | hdl × 17            |         |   |        |              |  |

| 0<br>answers     |                                                                                                                                                                                                      |         |              | first question. I will p                | provide soi | me resource |          |                         | 4.77           | verilog             | × 11    |   |        |              |  |

| 2 views          | riscv                                                                                                                                                                                                | chisel  | īpu          |                                         |             |             |          | lov 20 at 23:<br>apaj   | 47             | hardware            | × 11    |   |        |              |  |

| 2 views          |                                                                                                                                                                                                      |         |              |                                         |             |             | <u></u>  | 6 • 3                   |                |                     |         |   |        |              |  |

| 1                | Param                                                                                                                                                                                                | neteriz | ed FIFO in   | Chisel                                  |             |             |          |                         |                | sbt × 7<br>fpga × t | 5       |   |        |              |  |

| vote             | I was going through the Chisel 2.2 Tutorial manual (I am aware that Chisel3 is out in BETA version, but I am required to use Chisel2.2 for some extension of previously implemented modules). I have |         |              |                                         |             |             |          |                         | sion, but I am | digital-log         | ic × 5  |   |        |              |  |

| answers          | riscv                                                                                                                                                                                                | chisel  |              |                                         |             |             | asked N  | lov 18 at 9:3           | 3              | build ×             | 3       |   |        |              |  |

| 57 views         |                                                                                                                                                                                                      |         |              |                                         |             |             | 100      | Abhishek Tya<br>48 • 10 | agi            | uint × 3            |         |   |        |              |  |

|                  |                                                                                                                                                                                                      |         |              |                                         |             |             |          |                         |                | more relat          | ed tags |   |        |              |  |

#### Academic Impact: 188 citations (in 5 years)

#### Chisel: Constructing Hardware in a Scala Embedded Language

Jonathan Bachrach, Huy Vo, Brian Richards, Yunsup Lee, Andrew Waterman, Rimas Avižienis, John Wawrzynek, Krste Asanović EECS Department, UC Berkeley {jrb|buytbvo|richards/yunaup|vaterman|rimas|johnv|krste}becs.berkeley.edu

#### ABSTRACT

In this paper we introduce Check, a new hardware construction language that any apport advanced hardware design tailed highly parameterized generators and layered domain-specific gramming language, we raite the level of hardware design and strateful providing concepts including object orientation, functional programming, parameterized program, and type in accurate software simulator, or low-level Verding designed to map to other PFOA to a to astandard SIC flow for synthesis. This paper presents Check, its embedding in Stain, emuniton and XAC synthesis.

#### Categories and Subject Descriptors

B.6.3 [Logic Design]: [Design Aids – automatic synthesis, hardware description languages]

#### **General Terms**

Design, Languages, Performance

#### Keywords

CAD

#### 1. INTRODUCTION

The dominant traditional hardware-description languages (HDLs), Verilog and VHDL, were originally developed as hardware simulation languages, and were only later adopted as a basis for hardware symthesis. Because the semantics of these languages are based around simulation, synthesizable

<sup>\*</sup>Research supported by DoE Award DE-SC0003624, and by Microsoft (Award #024263) and Intel (Award #024894) funding and by matching funding by U.C. Discovery (Award #DIG07-10227).

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. DAC 2012, June 57, 2012, San Francisco, California, USA.

DAC 2012, June 3-7, 2012, San Francisco, California, USA. Copyright 2012 ACM 978-1-4503-1199-1/12/06 ...S10.00. chaiging must be inferred from a subset of the hangeage complexing tool devolptionset and defause exhaustion. These manageages also lack the powerful abstraction facilities that are common in moders software languages, which leads to low designer productively by making it difficult to remess composents. Contracting efficient lawiser using requires creachitectures [9] but these radiations and the lead of the module generation. The lead of the lead of the lead of the module generation to lead of the lead of the lead of the environment of the lead of the lead of the lead of the remeting of the lead of the lead of the lead of the lead of the tensor of the lead of the lead of the lead of the lead of the tensor of the lead of the lead of the lead of the lead of the tensor of the lead of the lead of the lead of the lead of the tensor of the lead of the lead of the lead of the lead of the tensor of the lead of the lead of the lead of the lead of the tensor of parameterized generaters facilities but still hack many powerful programming language facilities the still hack many powerful programming language facilities the still hack many

To work around these limitations, one common approach is to use another language as a macro processing language for an underlying HDL. For example, Genesis2 uses Perl to provide more flexible parameterization and elaboration of hardware blocks written in SystemVerilog [9]. The language called Verischemelog [6] provides a Scheme syntax for spec ifying modules in a similar format to Verilog. JHDL [] equates Java classes with modules. HML [7] uses standard ML functions to wire together a circuit. These approaches allow familiar and powerful languages to be macro languages for hardware netlists, but effectively require leaf components of the design to be described in the underlying HDL. This combined approach is cumbersome, combining the poor abstraction facilities of the underlying HDL with a completely different high-level programming model that does not understand hardware types and semantics.

An alternative approach is to begin from a domain-specific application programming language from which a hardware block is generated. Esterel [2] uses event-based statements to program hardware for reactive systems. DIL [4] is an intermediate language targeted at stream processing and hardware virtualization. Bluespec [3] supports a general concurrent computation model, based on guarded atomic actions While these can provide great designer productivity when the task in hand matches the pattern encoded in the appli cation programming model, they are a poor match for tasks outside their domain. For example, the design of a programmable microprocessor is not well described in a stream programming model, and guarded atomic actions are not a natural way to express a high-level DSP algorithm. Furthermore, in general it is difficult to derive an efficient microarchitecture from a higher-level computation model, especially if the goal is a programmable engine to run many applications, where the human designer would prefer to write a

Massachusetts Institute of Technology

UNIVERSITY of

WASHINGTON

#### Stanford University

Technical University of Denmark

# TEXAS TECH

# **D**NTNU

Norwegian University of Science and Technology

### Active Users (That We Know Of)

### Ideas for Governance? Maintenance? Workshops?

### Thanks to all Chiselers out there! (And many more!!)

# So long (ASPIRE), and thanks for all the fish chips!